【導(dǎo)讀】隨著工業(yè)4.0、自動駕駛、云計算等技術(shù)的飛速發(fā)展,其核心動力——系統(tǒng)級芯片(SoC)、FPGA和高端微處理器的集成度與算力持續(xù)攀升。這直接導(dǎo)致了供電需求的演變:電壓降至0.8V至1.1V,而單路電流需求卻可輕松突破30A。在為這些核心芯片提供動力的工業(yè)、汽車、服務(wù)器及通信設(shè)備中,電源設(shè)計已成為系統(tǒng)穩(wěn)定與能效的關(guān)鍵瓶頸。

引言:先進處理器的供電新范式

隨著工業(yè)4.0、自動駕駛、云計算等技術(shù)的飛速發(fā)展,其核心動力——系統(tǒng)級芯片(SoC)、FPGA和高端微處理器的集成度與算力持續(xù)攀升。這直接導(dǎo)致了供電需求的演變:電壓降至0.8V至1.1V,而單路電流需求卻可輕松突破30A。在為這些核心芯片提供動力的工業(yè)、汽車、服務(wù)器及通信設(shè)備中,電源設(shè)計已成為系統(tǒng)穩(wěn)定與能效的關(guān)鍵瓶頸。

傳統(tǒng)的電源方案已難以為繼。新一代電源解決方案必須同時滿足四大核心訴求:大電流輸出能力、極高的轉(zhuǎn)換效率、優(yōu)異的抗電磁干擾(EMI)性能,以及集成數(shù)字管理功能(如PMBus)以實現(xiàn)遙測與智能控制。本文將基于一款具代表性的40A雙相數(shù)字降壓穩(wěn)壓器,深入探討在實際設(shè)計中,如何通過優(yōu)化PCB布局和輸入電容配置,顯著提升效率與穩(wěn)定性。

效率為何成為首要技術(shù)指標?

我們以一個典型的應(yīng)用場景進行測算:輸入電壓12V,需輸出1V/30A為先進SoC內(nèi)核供電。若電源轉(zhuǎn)換效率為80%,那么總損耗功率高達7.5W。這些損耗最終以熱量的形式積聚,急劇抬升電源IC及其周邊元件(尤其是功率電感)的溫度。

在數(shù)據(jù)中心等環(huán)境溫度本身就可達40-50℃的應(yīng)用中,額外的7.5W損耗會使器件結(jié)溫快速逼近其典型的熱關(guān)斷閾值(150℃)。因此,對于這類負載點應(yīng)用,每提升1%的效率,都意味著系統(tǒng)熱管理的巨大改善和可靠性的顯著增強。

實戰(zhàn)優(yōu)化一:精雕細琢的SW節(jié)點PCB走線布局

PCB布局是影響開關(guān)電源效率的“隱形殺手”,尤其是在大電流路徑上。在早期的一款雙相器件演示板設(shè)計中,為了追求最優(yōu)的EMI性能,將兩相的電感采用了相對放置。雖然EMI表現(xiàn)良好,但代價是開關(guān)節(jié)點的PCB走線過長。

問題分析: 開關(guān)節(jié)點承載著高頻、大幅值的脈沖電壓與電流。過長的走線會引入可觀的寄生電阻。根據(jù)焦耳定律 P=I2R,導(dǎo)通損耗與電流的平方成正比。在20A至30A的大電流下,即便是毫歐級別的電阻也會產(chǎn)生瓦級的額外損耗。

優(yōu)化措施與數(shù)據(jù)對比:

通過對PCB進行優(yōu)化,將其中一相的電感旋轉(zhuǎn)90°并靠近IC放置,成功將SW節(jié)點走線長度從原先的約1.5cm縮短至0.3cm。經(jīng)計算,走線直流電阻從1.01mΩ降至約0.42mΩ。

實測結(jié)果:

熱成像對比: 優(yōu)化前,在20A負載下,SW節(jié)點走線區(qū)域溫升顯著,幾乎與IC本體相當。優(yōu)化后,該區(qū)域溫升明顯下降。

效率提升: 在12V轉(zhuǎn)0.6V,20A和30A負載條件下,效率分別提升了約0.4%和1.0%。在滿負載30A時,效率提升達1.5%,這意味著損耗降低了約0.53W。

結(jié)論: 在空間允許的前提下,應(yīng)優(yōu)先縮短大電流開關(guān)回路(特別是SW節(jié)點和GND)的走線長度與面積,這是實現(xiàn)高效率設(shè)計最直接有效的手段之一。

實戰(zhàn)優(yōu)化二:科學(xué)配置輸入電容,抑制振鈴與損耗

輸入電容的設(shè)計常被經(jīng)驗主義所誤導(dǎo),但其對效率和穩(wěn)定性的影響至關(guān)重要。輸入電容網(wǎng)絡(luò)是一個由不同電容構(gòu)成的協(xié)同系統(tǒng):

大容量電解電容: 用于應(yīng)對熱插拔浪涌電流。

大容量陶瓷電容: 通常為1206或1210封裝,用于平滑輸入電流紋波。

小容量高頻陶瓷電容: 如0402或0201封裝,用于濾除高頻噪聲。

封裝內(nèi)電容: 如Silent Switcher 2架構(gòu),將匹配的電容集成于封裝內(nèi)部,極大優(yōu)化高頻環(huán)路和EMI。

問題分析: 若總輸入電容不足或布局不當,在上管MOSFET導(dǎo)通的瞬間,巨大的瞬態(tài)電流會從輸入電容抽取電荷,導(dǎo)致輸入電壓發(fā)生跌落和振鈴。這與PCB走線及封裝的寄生電感形成LC諧振電路,不僅產(chǎn)生開關(guān)噪聲,還會增加開關(guān)器件的應(yīng)力與開關(guān)損耗,嚴重時甚至引發(fā)系統(tǒng)不穩(wěn)定。

優(yōu)化驗證:

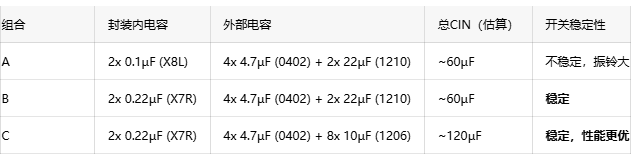

我們通過實驗對比了不同輸入電容組合(見表1)對性能的影響。

關(guān)鍵發(fā)現(xiàn):

穩(wěn)定性提升: 僅將封裝內(nèi)電容從0.1μF更換為0.22μF(組合A->B),即使總電容值變化不大,也足以顯著抑制SW節(jié)點振鈴,使系統(tǒng)恢復(fù)穩(wěn)定。

效率提升: 對比組合B和C,在負載電流為15A時,增加外部輸入電容使效率提升了約1.4%,對應(yīng)損耗降低0.3W。這是因為更大的電容有效抑制了輸入電壓的跌落,降低了開關(guān)損耗。

電容選型注意事項:

直流偏壓效應(yīng): 陶瓷電容的實際容值會隨其兩端直流電壓的升高而急劇下降。例如,一個額定值22μF的1206電容在12V直流偏壓下,實際容量可能僅剩不足10μF。而1210封裝的電容降額特性通常優(yōu)于1206。因此,對于12V輸入,優(yōu)先選用1210或更大尺寸的陶瓷電容。

溫度特性: 注意介電材料,如X7R電容的最高工作溫度為125℃,而X8L為150℃。在高溫環(huán)境應(yīng)用中,需確保電容在系統(tǒng)最高環(huán)境溫度下仍能正常工作。

仿真輔助設(shè)計:

使用SIMPLIS等仿真工具可以提前預(yù)判輸入電容配置的影響。通過建立包含寄生電感的降壓電路模型,可以清晰地觀察到,當輸入電容值翻倍后,SW節(jié)點的電壓振鈴幅度和輸入電壓的跌落得到明顯改善,為硬件設(shè)計提供了有力的理論依據(jù)。

總結(jié)

面向先進處理器的低壓大電流電源設(shè)計是一項復(fù)雜的系統(tǒng)工程。本文通過具體的測試數(shù)據(jù)與熱成像分析,揭示了優(yōu)化SW節(jié)點PCB走線和科學(xué)配置輸入電容對提升效率與穩(wěn)定性的決定性作用。在追求更高功率密度的今天,工程師需要跳出傳統(tǒng)經(jīng)驗,從器件物理特性、布局寄生參數(shù)到系統(tǒng)熱管理進行全鏈路精細化設(shè)計,方能打造出滿足未來算力需求的強大“能源心臟”。

推薦閱讀:

ADALM2000實驗指南:有源混頻器設(shè)計與轉(zhuǎn)換增益分析

技術(shù)雙雄聯(lián)手!逐點半導(dǎo)體與數(shù)字光芯共推Micro LED投影芯片升級